Modul 2 Percobaan 1

1. Jurnal [Kembali]

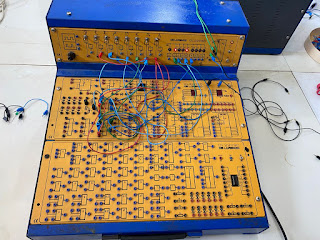

2. Alat dan Bahan [Kembali]

3. Rangkaian [Kembali]

- J-K Flip-Flop

Pada rangkaian J-K Flip-Flop di dalamnya juga terdapat R-S Flip-Flop, hal ini dikarenakan J-K Flip-Flop merupakan pengempangan dari R-S Flip Flop. Dimana sesuai dengan kondisi yang telah dipilih bahwasannya input masukan pada R dan S berlogika 0, maka disini R-S Flip-Flop akan aktif karena R-S Flip-Flop bekerja pada aktif low dan mengakibatkan J dan K tidak aktif, maka apapun yang dilakukan pada input J dan K tidak akan mempengaruhi output dari rangkaian tersebut. Dapat terlihat pada output bahwasannya dengan input R=0 dan S=0 maka akan menghasilkan ouput yang berlogika sama dengan ouput percobaan sebelumnya atau disebut sebagai kondisi tetap dimana output tidak mengalami perubahan.

- D Flip-Flop

Pada rangkaian D Flip-Flop sesuai dengan kodisi yang telah dipilih maka yang bekerja adalah R-S Flip-Flopnya karna input yang masuk berlogika 0, jadi apapun yang dilakukan pada input masukan D tidak akan mempengaruhi output dari rangkaiannya, jadi output tidak akan berubah sesuai dengan output sebelumnya, hal ini dinamakan dengan kodisi tetap atau output tanpa perubahan.

1. Bagaimana jika B0 dan B1 sama-sama diberi logika 0, apa yang terjadi pada rangkaian!

Jawab:

Berdasarkan pada percobaan yang telah dilakukan Ketika B0= 0 dan B1=0, maka akan dihasilkan output yang berlogika sama sesuai percobaan sebelumnya, hal ini dinamakan sebagai kondisi tetap atau output tanpa perubahan sesuai dengan table kebenaran.

2. 2. Bagaimana jika B3 diputuskan atau tidak dihubungkan pada rangkaian apa yang terjadi pada rangkaian?

Jawab:

Berdasarkan percobaan yang telah dilakukan, Ketika B3 yang merupakan clock diputuskan atau tidak dihubungkan pada rangkaian maka hal ini akan mengakibatkan J dan K tidak berfungsi meskipun R dan S tidak aktif, apapun yang dilakukan pada J dan K tidak akan mempengaruhi output. Karena J dan K tergantung pada terdapat clock atau tidak.

3. 3. Jelaskan apa yang dimaksud kondisi toggle, kondisi not change, dan kondisi terlarang dan flip-flop!

Jawab:

· Kondisi terlarang

Kondisi yang terjadi Ketika input sama-sama berlogika 1 atau pada percobaan 1 dapat dilihat pada percobaan no 3, dimana dihasilkan output Q=1 dan Q’=1, kondisi ini yang disebut sebagai kondisi terlarang dan sebisa dihindari selama percobaan karena dapat merusak alat.

· Kondisi not change

Kondisi ini terjadi Ketika input sama-sama berlogika 0, dimana akan dihasilkan output yang sama seperti percobaan sebelumnya, hal inilah yang disebut sebagai kondisi tanpa perubahan atau not change.

· Toggle

Kondisi ini terjadi jika input J=1 dan K=1, hal ini dapat dilihat pada percobaan 1 no 7, dimana output yang dihasilkan berubah-ubah. Hal inilah yang disebut sebagai toggle

- Download HTML: Klik disini

- Download Rangkaian Proteus: Klik disini

- Download Video: Klik disini

- Download IC JK Flip-Flop: Klik disini

- Download IC D Flip-Flop: Klik disini

- Download SW-SPDT: Klik disini

.png)

Tidak ada komentar:

Posting Komentar